PCIe设备概率性识别失败?这3个核心原因与排查思路

在嵌入式与服务器开发中,PCIe(PCI Express)接口早已成为连接高速外设的“标配”——小到PCIe无线网卡、SSD,大到FPGA加速卡、显卡,都依赖它实现高速数据传输。但不少工程师都会遇到一个棘手问题:PCIe设备有时能正常识别,有时却突然“失联”,这种概率性识别失败的故障,比必现故障更难排查,往往卡在硬件设计或调试环节浪费大量时间。

今天我们就从PCIe接口的核心原理入手,拆解开发中的关键注意事项,并针对“原理图一致性”“电感干扰”“串口电流倒灌”这三个高频故障点,给出具体的排查方案,帮你快速定位问题。

一、先搞懂:PCIe接口为什么能“高速又稳定”?

要排查识别失败问题,首先得明白PCIe的工作逻辑——它的“稳定”依赖硬件信号、供电、枚举流程的协同,任何一个环节的微小偏差,都可能导致“概率性故障”。

1. PCIe的核心架构:从“拓扑”到“枚举”

PCIe采用“点对点串行拓扑”,由根复合体(Root Comple

x,比如PU内的PCIe控制器)、端点设备(Endpoint,比如PCIe网卡)、交换机(Switch,扩展多设备)组成,每个设备通过“Lane(通道)”传输数据(常见x1/x4/x8/x16通道,通道数越多速度越快)。

而设备能否被识别,关键在于枚举流程:

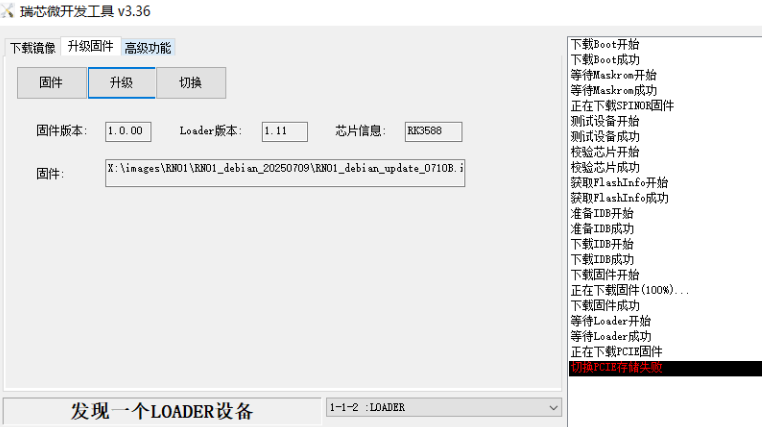

1.系统上电后,根复合体先初始化PCIe总线;

2.根复合体发送“枚举命令”,扫描总线上的端点设备;C

3.端点设备收到命令后,返回自身的“配置空间信息”(如设备ID、厂商ID、接口类型);

4.根复合体根据配置信息,为设备分配总线号、内存地址空间,完成识别。

整个过程对信号时序和供电稳定性要求极高——若信号延迟超标、供电电压波动,就可能导致枚举“偶发超时”,设备自然无法识别。

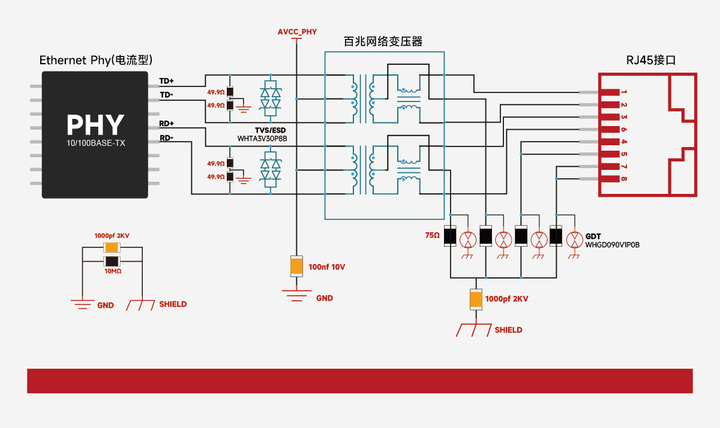

2. PCIe的信号与供电:“差分之美”与“电压红线”

•信号特性:PCIe用“差分信号”传输数据(一对反向的信号线,如TX+/-、RX+/-),这种设计能抵消外界干扰,但也对硬件设计提出严格要求:

差分对的线长必须匹配(误差通常要求≤5mm)、阻抗需严格控制(通常为100Ω±10%),若线长不匹配或阻抗突变,会导致信号反射,出现“时好时坏”的传输问题。

•供电要求:PCIe设备需要多种稳定电压供电(如12V主供电、3.3V辅助供电、1.8V/1.05V核心供电),且电压波动范围有明确限制(如12V允许±8%,3.3V允许±5%)。一旦供电电压跌落或出现尖峰噪声,设备可能无法完成初始化,导致识别失败。

二、开发避坑:PCIe硬件设计的3个“生死线”

概率性识别失败,90%的问题出在硬件设计阶段。在画原理图、做PCB时,这三个关键点必须严格把控,否则后期调试会陷入“无头苍蝇”状态。

1.严格遵循“官方参考设计”,拒绝“想当然修改”

PCIe控制器厂商(如Intel、AMD、Rockchip、Nvidia)会提供详细的“PCIe接口参考设计”,包括原理图、PCB布局指南、物料选型建议。很多工程师为了“简化设计”或“适配现有物料”,会私自修改原理图(比如更换复位芯片、调整供电电路),这往往是概率性故障的“埋雷点”。

比如某Rockchip平台开发中,工程师将PCIe复位信号的上拉电阻从4.7kΩ改为10kΩ,导致复位信号上升沿过缓,系统枚举时偶尔检测不到复位完成信号,设备就会“随机失联”。

核心原则:原理图中的“复位电路、供电时序电路、时钟电路、差分信号匹配电阻”,必须1:1对照官方参考设计,任何修改都需先与厂商FAE确认。

2.电感选型与布局:别让“滤波元件”变成“干扰源”

PCIe供电电路中,通常会用电感实现“滤波”和“储能”(比如在12V转3.3V的Buck电路中),但电感若选型不当或布局错误,会成为“信号干扰器”:

•选型错误:若电感的“寄生电容”“寄生电阻”过大,会在供电线上引入低频噪声,干扰PCIe设备的核心供电;

•布局错误:若电感靠近PCIe差分信号线(距离<3mm),电感工作时产生的磁场会耦合到差分信号中,破坏信号完整性,导致传输误码率升高,枚举偶尔失败。

避坑建议:优先选用厂商参考设计中推荐的电感型号(如TDK的SLF系列、Murata的LQM系列),且电感与PCIe差分信号线的距离需≥5mm,同时避免电感与差分对平行布局。

3. debug串口:别让“调试工具”变成“供电杀手”

很多工程师习惯在开发板上预留debug串口(如UART转USB),方便打印日志调试,但很少注意:串口接上电脑时,可能会发生“电流倒灌”,干扰PCIe供电。

原理很简单:电脑USB口的输出电压通常为5V/3.3V,而开发板上PCIe设备的辅助供电也是3.3V。若两者的“地电位”存在差异(比如电脑接地不良,开发板接外部电源),就会形成“电位差”,导致电流从USB口倒灌到PCIe的3.3V供电回路中——轻则导致PCIe供电电压被拉低(比如从3.3V跌到3.1V以下),重则烧毁供电芯片,直接让设备无法上电。

调试注意:

•接debug串口前,确认电脑与开发板的“地”是否共地(比如用万用表测两者的GND引脚,电位差应≤0.1V);

•若需独立供电(开发板用外部电源,电脑单独供电),建议在串口的VCC引脚串一个“二极管”(如SS14),防止电流倒灌。

三、实战排查:3个高频故障的定位方法

当遇到PCIe设备概率性识别失败时,不用盲目换设备、改代码,按以下步骤排查,能快速锁定问题。

1.排查“原理图一致性”:从源头排除设计缺陷

概率性故障若出现在批量生产阶段,先优先核对原理图与官方参考设计的差异:

•工具辅助:用Altium Designer、Cadence等工具的“原理图比较功能”,将自己的设计与官方参考图逐页对比,重点关注:

◦复位电路:复位芯片型号、上拉/下拉电阻阻值、复位延迟参数;

◦供电电路:电源芯片型号、电感/电容参数、电压反馈电阻阻值;

◦差分信号:是否有匹配电阻(通常为50Ω或100Ω)、电阻位置是否在靠近设备端(官方一般要求匹配电阻靠近端点设备,减少信号反射)。

•实物核对:对照BOM表,检查焊接的物料型号是否与原理图一致(比如电容容值、电阻阻值是否错焊),避免“原理图对了,但物料贴错了”的低级错误。

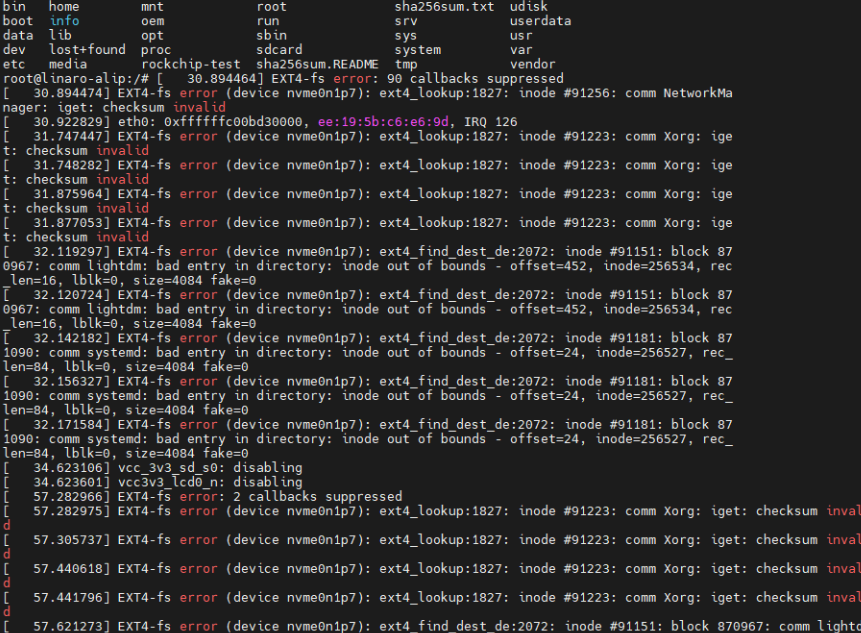

2.排查“电感干扰”:用示波器看信号“健康度”

若怀疑电感影响信号,可通过“信号测试”验证:

•测差分信号眼图:用示波器(需支持差分探头)连接PCIe的TX+/-或RX+/-信号,采集信号眼图——若眼图“眼高”不足(低于标准值的80%)、“眼宽”过窄,或存在明显的噪声尖峰,说明信号被干扰,需检查电感布局是否违规,或更换低寄生参数的电感。

•测供电噪声:用示波器测PCIe设备的3.3V辅助供电电压,若电压波动超过±5%(比如3.3V跌到3.1V以下),或存在频率在100kHz~1MHz的低频噪声,大概率是电感滤波效果差,需更换电感或增加滤波电容(如在供电端并联10μF+0.1μF的电容组合)。

3.排查“debug串口电流倒灌”:测供电电位差

若接上debug串口后,PCIe识别失败概率明显升高,可按以下步骤验证:

•断电测试:断开开发板外部电源,只接debug串口的USB线,用万用表测PCIe设备的3.3V供电引脚——若有电压(比如测到2.5V),说明存在电流倒灌(USB的3.3V通过串口倒灌到PCIe供电回路)。

•通电测试:接好开发板外部电源,再接debug串口,用示波器测PCIe的3.3V供电电压——若接上串口后,电压出现明显跌落(如从3.3V跌到3.0V),需在串口VCC引脚串二极管,或改用“只传数据、不供电”的串口线(断开USB的VCC引脚)。

四、总结:PCIe识别稳定的核心——“细节不妥协”

PCIe设备的概率性识别失败,看似“偶发”,实则是“硬件设计细节不到位”的必然结果。总结下来,关键就三句话:

1.参考设计别乱改:原理图、物料选型严格遵循厂商指南,不轻易“简化”或“替代”;

2.信号供电要盯紧:差分信号的线长、阻抗,供电的电压稳定性,用工具实测验证,不凭“感觉”判断;

3.调试环节防意外:debug串口、外部设备接入时,先考虑电位差、电流倒灌风险,避免“调试工具变故障源”。

其实PCIe接口的“稳定性”并不可怕,只要在设计初期把好“原理图、选型、布局”三关,调试时用工具精准定位,就能轻松避开概率性故障的坑。你在开发中还遇到过哪些PCIe识别问题?欢迎在评论区留言讨论!

- 随机文章

- 热门文章

- 热评文章

- 网传丨Intel 酷睿 Ultra 200K 系列 CPU 频率曝光:Ultra 9 285K 可达 5.7GHz

- 吃素会使人缺乏能量吗

- 免税店必买清单,科颜氏清洁泥膜上榜!

- 医师节丨家文化的温暖光芒,共筑生命之桥

- 2024全国青少年信息素养大赛总决赛圆满闭幕

- 喜欢戴耳塞、开灯睡觉?警惕这些伤害→

- 粤桂滇黔渝及华北东北地区有强降雨

- 如何科学减重?上海多学科专家携手为肥胖者开展个性化诊疗

- 林戈:中国生殖医学的四十年,实现从“能生”到“优生”迈进

- 追光动画于洲:为中国观众做中国故事

- 2024年“全国药品安全宣传周” 公众十大用药提示

- 第五届海峡客家中秋文艺晚会在“客家祖地”福建龙岩举办

- 科学用眼关注这五点 | 呵护眼健康

- 1《汉口路上》:勾连今昔的上海“荡马路”指南

- 2京东 明星送好礼 完成随机任务领随机京豆

- 3京东 满1500减120元优惠券,Plus会员可领~

- 4大众ID.3和ID.4 X聪明款上市,售价12.9888万起

- 5先领券再剁手:建设银行0.99元购36元立减金!中国银行充话费立减4元!

- 6“凯里酸汤”长桌宴,一场美食文化之旅

- 7“穿越”三千年的探寻,殷墟商文明何以流量不止?

- 8冬季,糖尿病患者如何控好血糖?生活方式干预能替代药物治疗吗?| 时令节气与健康

- 92024全国青少年信息素养大赛总决赛圆满闭幕

- 10京东百亿补贴、深圳专享、PLUS会员:Xiaomi 小米 13 ultra 16GB+512GB 黑色 第二代骁龙8

- 11《直播营销服务指南》国际标准入选2025年服贸会《服务贸易标准化示范案例》

- 12商业贸促会与贸易发展与标准合作组织(ODCCN)举行工作会谈

- 13激光焊接机在焊接防水电机的工艺流程

- 1crocs 卡骆驰 Literide 360 儿童户外拖鞋

- 2HELLY HANSEN 哈雷汉森 Odin 男子弹力夹克

- 3CHINA TELECOM 中国电信 封神卡 20年29元月租(135G全国流量+100分钟通话+自主激活)

- 4玩模总动员:让火焰净化一切!HEX 炎魔之王拉格纳罗斯 1/6 雕像 开箱

- 5可carry亦可辅助的果岭风扇

- 6QCY H3 主动降噪头戴蓝牙耳机

- 7好吃的巧克力排行前十名?哪种人气最高好吃?

- 8兰空图床,这个图床工具牛大啦!10分钟快速部署。

- 9不锈钢锅发黑怎么办?涂点这个东西,擦一擦,瞬间光亮如新

- 10【咖啡】1000元以下15台半自动咖啡机云选购攻略

- 11电脑技巧:推荐一款非常棒的截图软件X-Snip,值得收藏!

- 12“穷鬼天堂”,这些家居品,换个思路买,省下一个亿

- 13一键生成!4款超火视频自动生成器,你值得拥有!

新青年杂志

新青年杂志