体硅FinFET和SOI FinFET的差异

文章来源:半导体与物理

原文作者:jjfly686

本文简单介绍了体硅FinFET和SOI FinFET之间的结构差异与工艺差异。

在半导体制造领域,晶体管结构的选择如同建筑中的地基设计,直接决定了芯片的性能上限与能效边界。当制程节点推进到22nm以下时,传统平面晶体管已无法满足需求,鳍式场效应晶体管(FinFET) 以其三维立体结构成为行业主流。然而在FinFET阵营内部,一场关于“地基材料”的技术路线竞争悄然展开——这便是Bulk Silicon(体硅) 与SOI(绝缘体上硅) 两大技术的对决。这场对决不仅关乎性能极限的突破,更牵动着芯片成本与可靠性的微妙平衡,成为半导体行业持续演进的关键战场。

结构差异:从物理基础看技术分野

Bulk Silicon FinFET:深槽隔离的工程杰作

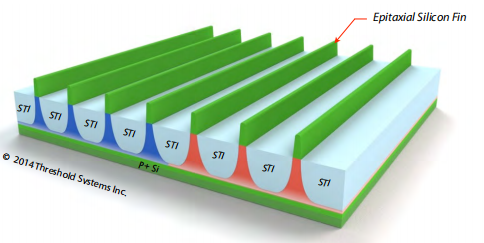

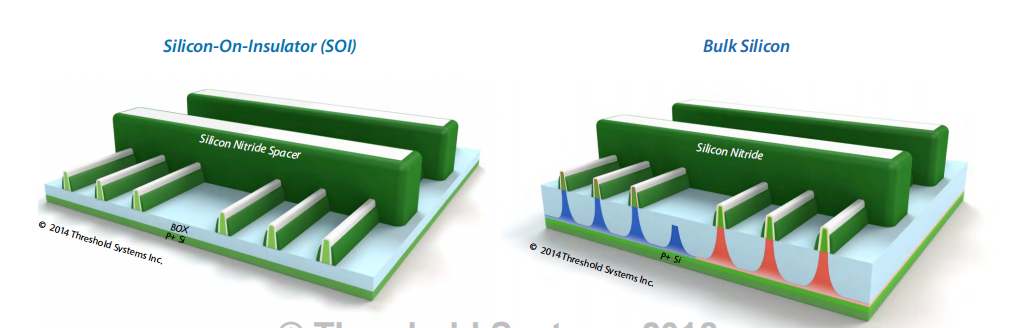

Bulk Silicon FinFET基于常规硅晶圆制造,其核心挑战在于如何在导电的硅衬底上实现相邻晶体管间的有效隔离。为实现这一目标,工程师们开发了浅沟槽隔离(STI) 技术:通过等离子刻蚀在硅衬底上挖出深达数百纳米的沟槽;填充二氧化硅(SiO₂) 或氮化硅(Si₃N₄) 作为绝缘材料;在隔离区域之间形成垂直硅鳍(典型高度30-50nm,宽度5-10nm);栅极从三面包裹硅鳍,增强沟道控制能力。

这一结构的复杂性在截面图中显露无遗:硅鳍底部与衬底直接相连,需要通过精密掺杂在鳍基形成隔离层,防止漏电流向衬底扩散。随着鳍高度的增加,掺杂均匀性控制成为难点,可能引发随机掺杂涨落(RDF) 导致的阈值电压波动。

SOI FinFET:天然绝缘的优雅设计

SOI FinFET则构建在特殊的三层晶圆上:顶层硅(~10nm):用于刻蚀形成晶体管鳍片;埋氧层(BOX)(~25nm):二氧化硅绝缘层,隔绝衬底;基底硅:仅起机械支撑作用。

这种结构带来了革命性简化:无需STI刻蚀:埋氧层自然隔离相邻器件;消除鳍基掺杂:BOX层阻挡垂直漏电路径;硅鳍全耗尽:超薄顶层硅确保栅极完全控制沟道。

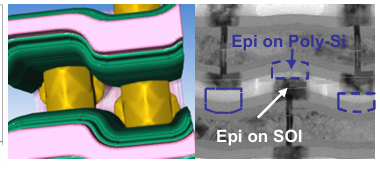

从电子显微镜图像可见,SOI FinFET的硅鳍如精致的雕塑般矗立在光滑的氧化层上,与Bulk Silicon中复杂的隔离结构形成鲜明对比。

| 衬底材料 | 单层硅晶圆 | 硅/二氧化硅/硅复合晶圆 |

| 隔离方式 | 浅沟槽隔离(STI) | 埋氧层(BOX)天然隔离 |

| 硅鳍连接 | 与衬底直接相连 | 通过BOX层与衬底绝缘 |

| 鳍高 | 30-50nm | 20-40nm |

| 关键掺杂区 | 鳍基防漏电掺杂层 | 无需特殊掺杂 |

| 特性 | Bulk Silicon FinFET | SOI FinFET |

|---|

工艺复杂度:从制造流程看成本控制

Bulk Silicon FinFET:繁琐但成熟的前端工艺

Bulk Silicon FinFET的制造前端包含多个高精度步骤:

1、深槽刻蚀:反应离子刻蚀(RIE)形成STI沟槽,深宽比达5:1以上;

2、隔离填充:原子层沉积(ALD)氮化硅+二氧化硅填充沟槽;

3、化学机械抛光(CMP):去除多余隔离材料,实现全局平坦化;

4、鳍基注入:倾斜离子注入形成P/N阱与防穿通掺杂层;

5、硅鳍刻蚀:多重曝光光刻+刻蚀定义鳍阵列;

这些步骤不仅增加5-7道光罩,更引入掺杂均匀性和刻蚀深宽比等控制难点。特别是鳍基注入环节,需精确控制掺杂轮廓以平衡泄漏与性能,退火过程易导致杂质扩散,影响阈值电压稳定性。

SOI FinFET:简化的前端流程

SOI工艺大幅简化前端制程:

跳过STI:BOX层已实现天然隔离,仅需定义有源区图形;

省略鳍基注入:埋氧层阻断漏电,无需复杂掺杂工程;

直接鳍刻蚀:在超薄顶层硅上一步形成全耗尽硅鳍;

这种简化使SOI FinFET的前端工艺步骤减少约30%,显著降低成本。

- 随机文章

- 热门文章

- 热评文章

- Backcountry MTN Air 男女同款长裤

- 看激烈奥运赛事,它是我的压惊神器!

- 中新健康|国家医保局:2023年监测的农村低收入人口参保率持续稳定在99%以上

- 中新健康|国家医保局:进一步优化职工医保个人账户共济政策 放宽共济范围

- 适合新手铲屎官养的十大宠物猫

- 西北地区东部华北等地将有一次降水过程 南方大部将有持续性高温天气

- 华北东北等地暴雨如注 南方高温闷热天气增多增强

- 如何以大规模设备更新促进县域医疗高质量发展?多名专家建言献策

- 一个飞行员,和“330”较上劲了!

- 医疗援藏30年 援助方与受援方共同守护西藏民众健康生命线

- 秋季容易情绪低落,如何进行自我调适 | 时令节气与健康

- 海南电网恢复与南方电网主网联通

- “十一”假期长线旅游市场热度攀升 “体育+旅游”激活文旅消费新引擎

- 1《汉口路上》:勾连今昔的上海“荡马路”指南

- 2京东 明星送好礼 完成随机任务领随机京豆

- 3京东 满1500减120元优惠券,Plus会员可领~

- 4大众ID.3和ID.4 X聪明款上市,售价12.9888万起

- 5先领券再剁手:建设银行0.99元购36元立减金!中国银行充话费立减4元!

- 6“凯里酸汤”长桌宴,一场美食文化之旅

- 7“穿越”三千年的探寻,殷墟商文明何以流量不止?

- 8冬季,糖尿病患者如何控好血糖?生活方式干预能替代药物治疗吗?| 时令节气与健康

- 92024全国青少年信息素养大赛总决赛圆满闭幕

- 10京东百亿补贴、深圳专享、PLUS会员:Xiaomi 小米 13 ultra 16GB+512GB 黑色 第二代骁龙8

- 11《直播营销服务指南》国际标准入选2025年服贸会《服务贸易标准化示范案例》

- 12商业贸促会与贸易发展与标准合作组织(ODCCN)举行工作会谈

- 13激光焊接机在焊接防水电机的工艺流程

- 1crocs 卡骆驰 Literide 360 儿童户外拖鞋

- 2HELLY HANSEN 哈雷汉森 Odin 男子弹力夹克

- 3CHINA TELECOM 中国电信 封神卡 20年29元月租(135G全国流量+100分钟通话+自主激活)

- 4玩模总动员:让火焰净化一切!HEX 炎魔之王拉格纳罗斯 1/6 雕像 开箱

- 5可carry亦可辅助的果岭风扇

- 6QCY H3 主动降噪头戴蓝牙耳机

- 7好吃的巧克力排行前十名?哪种人气最高好吃?

- 8兰空图床,这个图床工具牛大啦!10分钟快速部署。

- 9不锈钢锅发黑怎么办?涂点这个东西,擦一擦,瞬间光亮如新

- 10【咖啡】1000元以下15台半自动咖啡机云选购攻略

- 11电脑技巧:推荐一款非常棒的截图软件X-Snip,值得收藏!

- 12“穷鬼天堂”,这些家居品,换个思路买,省下一个亿

- 13一键生成!4款超火视频自动生成器,你值得拥有!

新青年杂志

新青年杂志